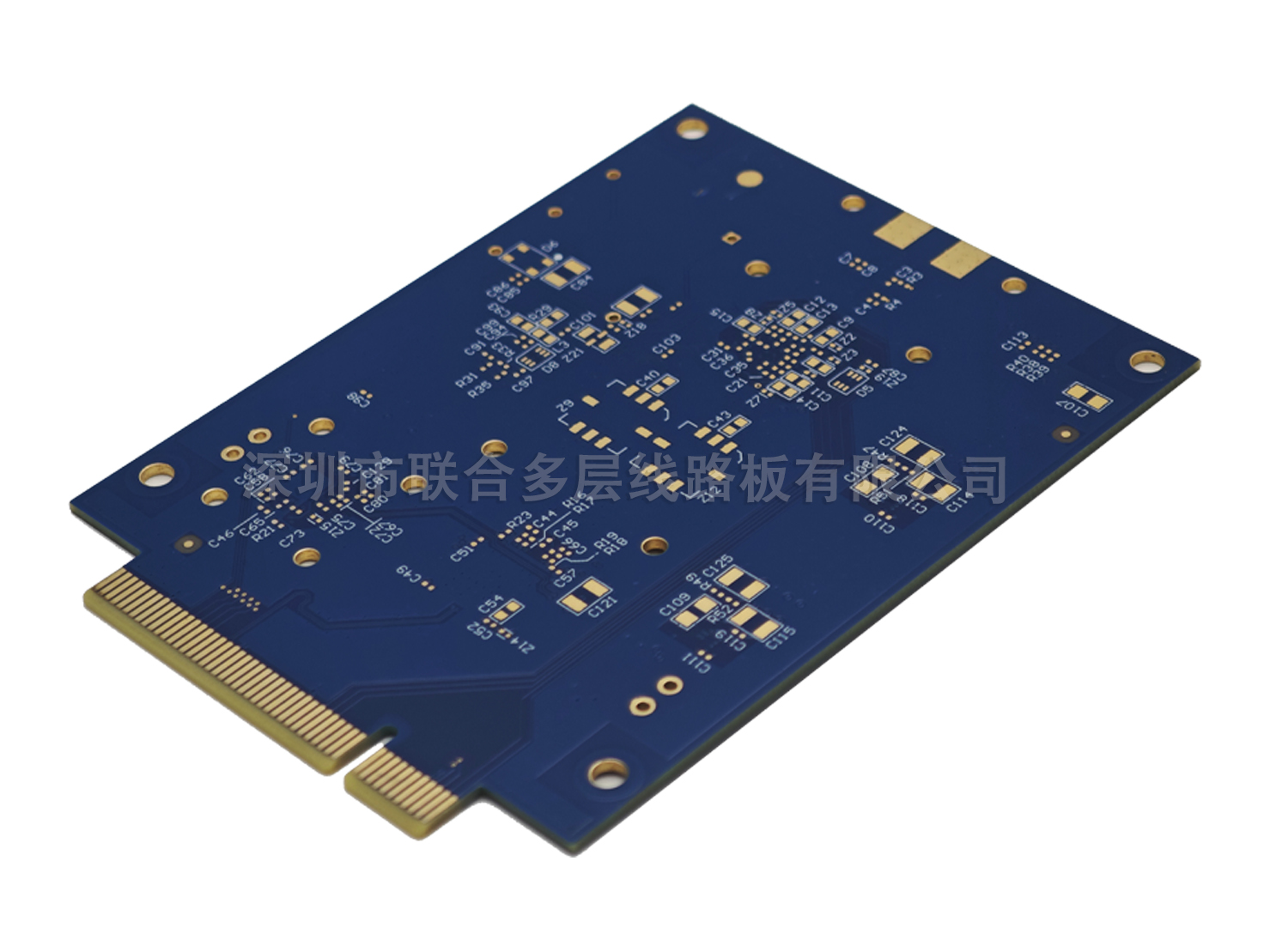

PCB 阻抗控制層設計對 grounding 焊盤上錫的影響

在 PCB 線路板設計中,阻抗控制層與接地焊盤上錫質量看似分屬不同技術領域,實則存在密切關聯。阻抗控制層通過精確設計線路尺寸、介質厚度和材料特性,確保信號傳輸的完整性,而接地焊盤上錫則直接影響電路的電氣連接可靠性與散熱性能。兩者的設計交互可能通過結構布局、工藝參數和材料選擇三個維度產生影響,成為線路板質量控制的關鍵環節。

從結構布局來看,阻抗控制層的布線密度與接地焊盤的位置安排可能引發上錫隱患。為滿足高頻信號的阻抗要求(如 50Ω 或 100Ω 差分阻抗),線路常采用細間距平行布線,這可能導致接地焊盤周圍的銅箔面積受限。某 5G 基站主板的阻抗控制線路與接地焊盤間距只 0.2mm,在回流焊過程中,焊錫因表面張力向密集線路擴散,導致焊盤上錫量不足,出現 “虛焊” 現象,經檢測此類缺陷的導通電阻比標準值高 3 倍以上。此外,阻抗控制層的過孔設計若過于靠近接地焊盤(距離<0.5mm),可能形成焊錫流動通道,造成焊盤 “拉尖” 或 “橋連”,某路由器主板因此類問題導致接地電阻波動達 ±20%。

從結構布局來看,阻抗控制層的布線密度與接地焊盤的位置安排可能引發上錫隱患。為滿足高頻信號的阻抗要求(如 50Ω 或 100Ω 差分阻抗),線路常采用細間距平行布線,這可能導致接地焊盤周圍的銅箔面積受限。某 5G 基站主板的阻抗控制線路與接地焊盤間距只 0.2mm,在回流焊過程中,焊錫因表面張力向密集線路擴散,導致焊盤上錫量不足,出現 “虛焊” 現象,經檢測此類缺陷的導通電阻比標準值高 3 倍以上。此外,阻抗控制層的過孔設計若過于靠近接地焊盤(距離<0.5mm),可能形成焊錫流動通道,造成焊盤 “拉尖” 或 “橋連”,某路由器主板因此類問題導致接地電阻波動達 ±20%。

工藝參數的匹配性是另一重要影響因素。阻抗控制層通常要求基材具有穩定的介電常數(如 FR-4 的 Dk 值 4.2±0.2),這類基材的表面能較低(約 38dyn/cm),若未進行有效的表面處理,接地焊盤的可焊性會下降。某消費電子廠商的測試顯示,未經等離子處理的阻抗控制板,接地焊盤上錫率只 82%,而處理后提升至 99.5%。同時,阻抗線路的蝕刻精度要求(線寬偏差≤±0.02mm)可能導致接地焊盤邊緣的銅箔殘留,形成 “毛刺”,阻礙焊錫均勻鋪展,此類缺陷在 AOI 檢測中的識別率需達到 100%,否則將影響接地可靠性。

材料選擇的協同性也不容忽視。為降低高頻損耗,阻抗控制層常采用低粗糙度銅箔(Rz≤1.5μm),但這類銅箔與焊錫的結合力弱于常規銅箔。對比測試表明,低粗糙度銅箔的接地焊盤在 100 次熱循環后,焊錫剝離強度下降 15%,而普通銅箔只下降 5%。因此在汽車電子等可靠性要求高的領域,常采用 “低粗糙度銅箔 + 化學鍍鎳金” 的復合方案,通過鎳層增強結合力,使焊盤上錫后的熱沖擊耐受性提升至 260℃/10 秒無脫落。

設計優化可有效規避潛在風險。采用 “接地焊盤隔離環” 設計,在阻抗線路與焊盤間預留 0.3mm 以上的空白區域,配合阻焊油墨開窗控制(開窗尺寸比焊盤大 0.1mm),可引導焊錫精確附著。某工業控制板通過此方案,接地焊盤上錫良率從 89% 提升至 99.2%。對于高頻場景,采用 “共面波導” 結構的阻抗控制設計,將接地平面延伸至焊盤邊緣,既保證阻抗匹配(偏差≤±10%),又增加焊盤散熱面積,使上錫后的焊點溫度降低 12℃。此外,選擇介電常數與可焊性平衡的基材(如 Megtron 6 的 Dk 值 3.6±0.1,表面能 42dyn/cm),可在滿足阻抗要求的同時提升焊盤潤濕性。

在線路板制造流程中,需建立針對性的質量管控體系:阻抗測試時同步檢測接地焊盤區域的銅箔粗糙度(Ra≤0.3μm);回流焊前通過菲針測試驗證焊盤與接地平面的導通性;上錫后采用 X 射線檢測焊點厚度(標準 0.8-1.2mm)和空洞率(≤5%)。某通信設備廠商通過這套體系,將阻抗控制板的接地焊盤不良率從 3.5% 降至 0.3%。

行業行家指出,隨著高速信號技術的發展(如 PCIe 6.0 的 32Gbps 傳輸),阻抗控制與上錫質量的協同設計將愈發重要。未來可通過仿真軟件提前模擬焊錫流動與阻抗特性的相互影響,在設計階段優化布局參數,實現電氣性能與工藝可靠性的雙重保障。對于線路板企業而言,建立跨部門的協同機制(設計、工藝、質量),是解決此類交叉技術問題的關鍵所在。