-

寧夏電氣完整性系列

寧夏電氣完整性系列電路板的PCB布局對電氣完整性測試有很大的影響。電路板的布局應該合理,遵循一定的設計規則,具有良好的地面引線、電源引線等,這些都是為了減小電路板的噪聲干擾、提升電路板的信號完整性。如果電路板的布局不合理或者違反了設計規則,會導致電路中易受干擾、噪聲信號干擾等問...

2024-03-01 -

遼寧高速電路測試

遼寧高速電路測試高速電路測試是一個非常重要的領域,主要目的是測試高速電路的電特性、時序特性、邏輯特性和功耗等多個方面,以確保高速電路的性能和可靠性。以下是一些與高速電路測試相關的問題和信息: 1.什么是高速電路測試?高速電路測試是指應用多種測試技術對高速電路的性能和...

2024-02-29 -

信號完整性測試電氣完整性銷售價格

信號完整性測試電氣完整性銷售價格為了檢測電路中的信號完整性問題,需要采用適當的電氣完整性測試方法。以下是一些常用的測試方法: 1.時域反射測試(TDR) 時域反射測試是一種通過發送一個脈沖信號,然后測量信號反射來確定電路中反射點的位置的方法。通過時域反射測試,可以判斷是否存在...

2024-02-28 -

浙江數字信號以太網測試

浙江數字信號以太網測試以太網交換機是基于以太網傳輸數據的交換機,以太網采用共享總線型傳輸媒體方式的局域網。以太網交換機的結構是每個端口都直接與主機相連,并且一般都工作在全雙工方式。交換機能同時連通許多對端口,使每一對相互通信的主機都能像獨占通信媒體那樣,進行無地傳輸數據。 ...

2024-02-27 -

南山區HDMI測試LPDDR4信號完整性測試

南山區HDMI測試LPDDR4信號完整性測試LPDDR4并不支持高速串行接口(HSI)功能。相反,LPDDR4使用的是并行數據接口,其中數據同時通過多個數據總線傳輸。LPDDR4具有64位的數據總線,每次進行讀取或寫入操作時,數據被并行地傳輸。這意味著在一個時鐘周期內可以傳輸64位的數據。與高速串行接口...

2024-02-26 -

測量LPDDR4信號完整性測試系列

測量LPDDR4信號完整性測試系列時鐘和信號的匹配:時鐘信號和數據信號需要在電路布局和連接中匹配,避免因信號傳輸延遲或抖動等導致的數據傳輸差錯。供電和信號完整性:供電電源和信號線的穩定性和完整性對于精確的數據傳輸至關重要。必須保證有效供電,噪聲控制和良好的信號層面表現。時序參數設置:在系統設計...

2024-02-25 -

測試服務LPDDR4信號完整性測試產品介紹

測試服務LPDDR4信號完整性測試產品介紹時鐘和信號的匹配:時鐘信號和數據信號需要在電路布局和連接中匹配,避免因信號傳輸延遲或抖動等導致的數據傳輸差錯。供電和信號完整性:供電電源和信號線的穩定性和完整性對于精確的數據傳輸至關重要。必須保證有效供電,噪聲控制和良好的信號層面表現。時序參數設置:在系統設計...

2024-02-24 -

南沙區設備LPDDR4信號完整性測試

南沙區設備LPDDR4信號完整性測試電路設計要求:噪聲抑制:LPDDR4的電路設計需要考慮噪聲抑制和抗干擾能力,以確保穩定的數據傳輸。這可以通過良好的布線規劃、差分傳輸線設計和功耗管理來實現。時序和延遲校正器:LPDDR4的電路設計需要考慮使用適當的時序和延遲校正器,以確保信號的正確對齊和匹配。...

2024-02-23 -

鹽田區PCI-E測試LPDDR4信號完整性測試

鹽田區PCI-E測試LPDDR4信號完整性測試LPDDR4具備多通道結構以實現并行存取,提高內存帶寬和性能。LPDDR4通常采用雙通道(DualChannel)或四通道(QuadChannel)的配置。在雙通道模式下,LPDDR4的存儲芯片被分為兩個的通道,每個通道有自己的地址范圍和數據總線。控制器可以同...

2024-02-22 -

羅湖區眼圖測試LPDDR4信號完整性測試

羅湖區眼圖測試LPDDR4信號完整性測試相比之下,LPDDR3一般最大容量為8GB。低功耗:LPDDR4借助新一代電壓引擎技術,在保持高性能的同時降低了功耗。相比于LPDDR3,LPDDR4的功耗降低約40%。這使得移動設備能夠更加高效地利用電池能量,延長續航時間。更高的頻率:LPDDR4的工作頻率...

2024-02-21 -

福田區物理層測試LPDDR4信號完整性測試

福田區物理層測試LPDDR4信號完整性測試LPDDR4并不支持高速串行接口(HSI)功能。相反,LPDDR4使用的是并行數據接口,其中數據同時通過多個數據總線傳輸。LPDDR4具有64位的數據總線,每次進行讀取或寫入操作時,數據被并行地傳輸。這意味著在一個時鐘周期內可以傳輸64位的數據。與高速串行接口...

2024-02-20 -

廣東信號完整性分析PCI-E測試

廣東信號完整性分析PCI-E測試傳輸線理論基礎與特征阻抗 傳輸線理論實際是把電磁場轉換為電路的分析來簡化分析的手段,分布式元件的傳輸線 電路模型傳輸線由一段的RLGC元件組成。 為了更簡便地分析傳輸線,引入特征阻抗的概念,由特征阻抗來進行信號傳輸的分析。 將傳輸線等效成分段電...

2024-02-19 -

上海眼圖測試電氣完整性

上海眼圖測試電氣完整性電氣完整性測試是用于評估電路信號完整性和電源完整性的測試方法,其基本原理是通過注入信號并觀察信號的響應來評估電路的性能。 以下是一些常見的電氣完整性測試方法及其原理: 1. 時域反射測試(TDR):TDR是一種通過向線路注入脈沖信號來檢測線路中...

2024-02-18 -

浙江高速電路測試聯系方式

浙江高速電路測試聯系方式高速電路測試在現代電子系統設計和制造中起著至關重要的作用。因為高速電路具有很高的傳輸速率,因此要求測試過程具有較高的準確性、精度和穩定性,以確保高速電路可以穩定并正確地傳輸信號。 高速電路測試中需要測量的參數包括信號完整性、信號失真、串擾、接口規范和...

2024-02-18 -

廣東高速電路測試聯系方式

廣東高速電路測試聯系方式高速電路測試在現代電子系統設計和制造中起著至關重要的作用。因為高速電路具有很高的傳輸速率,因此要求測試過程具有較高的準確性、精度和穩定性,以確保高速電路可以穩定并正確地傳輸信號。 高速電路測試中需要測量的參數包括信號完整性、信號失真、串擾、接口規范和...

2024-02-18 -

數字信號電氣完整性檢查

數字信號電氣完整性檢查電氣完整性測試關注的是電路中信號的傳輸和接收特性,主要是為了保證電路和系統在操作時可以正常地進行信號傳輸和接收,減少信號傳輸的錯誤和干擾。而其他測試方法可能關注的是電路和系統的其他性能指標,例如功耗、速度、精度等。 舉例來說,功能測試關注的是設備或系...

2024-02-08 -

江蘇眼圖測量信號完整性測試

江蘇眼圖測量信號完整性測試眼圖概念 眼圖是指利用實驗的方法估計和改善(通過調整)傳輸系統性能時在示波器上觀察到的一種圖形。觀察眼圖的方法是:用一個示波器跨接在接收濾波器的輸出端,然后調整示波器掃描周期,使示波器水平掃描周期與接收碼元的周期同步,這時示波器屏幕上看到的圖形像人的...

2024-02-08 -

甘肅USB測試高速電路測試

甘肅USB測試高速電路測試高速電路信號完整性的測試方法主要包括以下幾種: 1.眼圖測試法(EyeDiagramTesting):這種方法是通過采集信號的眼圖數據,利用眼球的開口度、高度、位置等參數來評估信號完整性。 2.時域反射法(Time-DomainReflecto...

2024-02-08 -

寧夏高速電路測試檢查

寧夏高速電路測試檢查1.測試需求分析 在進行高速電路測試前,需要對測試需求進行充分的分析和評估。測試需求分析的目的是為了確定需測試的電路的基本特性、測試方法和測試標準。具體包括:電路的基本特性(如工作頻率、帶寬、比較大時延等)、電路的測試目標(如電學性能、時序特性、功耗...

2024-02-07 -

寧夏USB測試眼圖測量

寧夏USB測試眼圖測量信號上升時間與下降時間 一般測量上升及下降時間是以眼圖占20%~80%的部分為主,其中上升時間如下圖,分別以左側交叉點左側(20%)至右側(80%)兩塊水平區間作此傳遞信號上升斜率時間之換算,計算公式如下: 上升時間=平均(80%時間位準)-平...

2024-02-07 -

設備電氣完整性價格優惠

設備電氣完整性價格優惠電氣完整性測試是用于評估電路信號完整性和電源完整性的測試方法,其基本原理是通過注入信號并觀察信號的響應來評估電路的性能。 以下是一些常見的電氣完整性測試方法及其原理: 1. 時域反射測試(TDR):TDR是一種通過向線路注入脈沖信號來檢測線路中...

2024-02-07 -

山東電氣完整性市場價

山東電氣完整性市場價3.電源完整性分析:通過建立電源電路的仿真模型,使用仿真軟件進行分析,以評估電源的質量、穩定性和紋波等參數是否與設計要求相符。 4. 環境完整性分析:分析電路在不同環境下的工作情況,例如并排布線帶來的相互干擾、溫度和濕度變化等因素的影響,以確定是否需...

2024-02-06 -

通信MIPI測試聯系方式

通信MIPI測試聯系方式MIPI-DSI接口以MIPID-PHY協議定義的物理傳輸層為基礎,DPHY定義的物理傳輸層多可支持4個數據通道,1個時鐘通道,每個通道在低功耗模式時以1.2V的低速信號傳輸,在高速模式時則采用擺幅為200毫伏的低壓差分信號傳輸,從而相對于現有的設備表現出更高...

2024-02-06 -

貴州DDR一致性測試方案商

貴州DDR一致性測試方案商克勞德高速數字信號測試實驗室 DDR SDRAM即我們通常所說的DDR內存,DDR內存的發展已經經歷了五代,目前 DDR4已經成為市場的主流,DDR5也開始進入市場。對于DDR總線來說,我們通常說的 速率是指其數據線上信號的快跳變速率。比如3200M...

2024-02-06 -

新疆高速電路測試一致性測試

新疆高速電路測試一致性測試4.頻率響應技術頻率響應技術通常用于測量電路在不同頻率下的響應特性,并評估其性能和可靠性。在高速電路測試中,頻率響應技術通常使用頻譜分析儀、高速示波器和信號發生器等儀器進行。 5. 信號完整性技術信號完整性技術是評估高速電路傳輸信號質量的一種方法。這...

2024-02-05 -

遼寧信號完整性分析一致性測試

遼寧信號完整性分析一致性測試邊沿時間會影響信號達到翻轉門限電平的時間,并決定信號的帶寬。 信號之間的偏移(Skew),指一組信號之間的時間偏差,主要是由于在信號之間傳輸路 徑的延時(傳輸延遲)不同及一組信號的負載不同,以及信號的干擾(串擾)或者同步開關 噪聲所造成信號上升下降時...

2024-02-05 -

河北高速電路測試一致性測試

河北高速電路測試一致性測試高速電路測試是現代電子系統設計和制造過程中必不可少的一個環節。高速電路具有極高的傳輸速率和復雜性,因此測試過程需要具有較高的精度、準確性和穩定性,才能保證電路在傳輸信號時可以保持良好的信號完整性、避免信號失真、減少串擾和故障,并符合接口規范和電磁兼容性要求...

2024-02-05 -

廣東物理層測試eDP信號完整性測試協議測試方法

廣東物理層測試eDP信號完整性測試協議測試方法評估eDP物理層信號完整性常需要進行以下測試和分析:信號電平測量:使用示波器或邏輯分析儀等設備來測量信號的電平,并確保其符合規范要求。時域分析:使用時域分析器觀察信號的波形變化、毛刺和幅度失真等情況。眼圖分析:使用眼圖儀器來展示信號眼圖,包括開口寬度和形狀等參...

2024-02-04 -

云南高速電路測試銷售價格

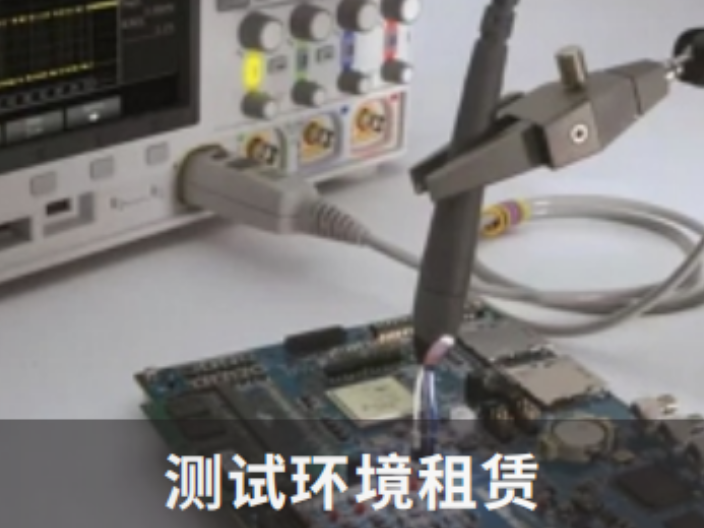

云南高速電路測試銷售價格三、測試工具 高速電路測試需要使用一系列的測試工具和測試設備,常見的測試工具包括示波器、頻譜分析儀、網絡分析儀、信號發生器、信號分析儀等。這些工具可以用來測試電路的信號電氣特性,包括電壓、電流、頻率、相位等參數。同時,還可以通過這些工具進行數據采集、...

2024-02-04 -

四川高速電路測試安裝

四川高速電路測試安裝3.信噪比測試:對數字通信電路進行信噪比測試,以確定其在一定信噪比下能夠正常工作的比較高速率。通常使用頻譜分析儀、信號發生器等測試儀器進行測試。 4.誤碼率測試:對數字通信電路的誤碼率進行測試,以確定其在一定速率下可容忍的誤碼率范圍。通常使用誤碼率測...

2024-02-04