-

荊州定制PCB設計銷售電話

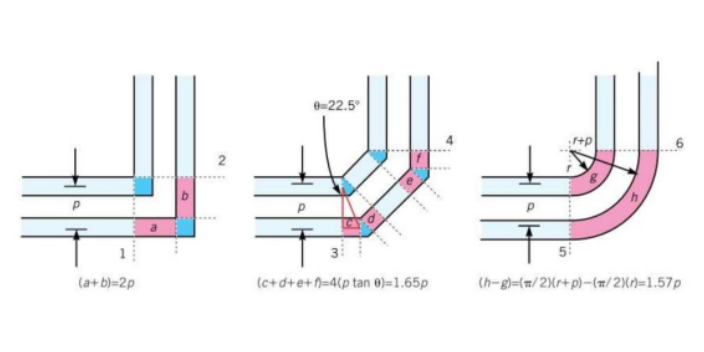

荊州定制PCB設計銷售電話PCB(印刷電路板)設計是電子產品開發中的**環節,其質量直接影響產品的性能、可靠性與生產效率。以下從設計流程、關鍵原則及常見挑戰三個方面展開分析:一、設計流程的標準化管理PCB設計需遵循嚴格的流程:需求分析與原理圖設計:明確電路功能需求,完成原理圖繪制,...

2025-07-15 -

鄂州生產PCB制版加工

鄂州生產PCB制版加工在制板完成后,工程師們還需進行多重測試,確保每一個線路都能正常工作。無論是電氣測試還是功能測試,都會嚴謹細致地進行,確保**終產品的質量與可靠性。通過這些嚴格的檢測步驟,PCB制板不僅能滿足客戶的需求,更能在激烈的市場競爭中脫穎而出。此外,隨著智能科技的快速發...

2025-07-14 -

鄂州印制PCB制版加工

鄂州印制PCB制版加工4.2 設計規則遵循在 PCB 設計過程中,嚴格遵循設計規則是確保電路板可制造性和性能的關鍵。設計規則涵蓋了眾多方面,如線寬與線距的最小值、過孔的尺寸與類型、焊盤的形狀與大小等。不同的制版廠由于設備和工藝水平的差異,可能會有略微不同的設計規則要求。一般來說,線...

2025-07-14 -

襄陽印制PCB制版加工

襄陽印制PCB制版加工在完成制版后,緊接著要進行的一項至關重要的工作是測試。無論是功能性測試還是可靠性測試,所有的PCB都必須經過嚴格的檢驗,以確保其在實際使用時能夠長期穩定地發揮作用。這不僅涉及到設備的性能,更直接關系到用戶的使用體驗和安全。然而,在這看似繁瑣的過程背后,還有許多...

2025-07-14 -

荊州打造PCB制版原理

荊州打造PCB制版原理印刷電路板(PCB)制版是電子產品制造過程中至關重要的一環,經過多年的發展,PCB制版技術已逐漸成熟,成為現代電子設備不可或缺的基礎。它不僅*是一個承載電子元件的載體,更是連通電路、實現功能的重要橋梁。制版的過程涵蓋了從設計到成品的一系列復雜流程,包括電路設計...

2025-07-14 -

如何PCB培訓功能

如何PCB培訓功能培訓內容PCB培訓內容通常包括以下幾個方面:基礎知識PCB的定義、分類及生產工藝流程。常用電子元器件的識別及電路原理圖的理解。設計軟件操作掌握Cadence OrCAD Capture、PADS Logic及PADS PCB、Polar Si9000等PCB設...

2025-07-14 -

武漢打造PCB制版原理

武漢打造PCB制版原理總結來說,PCB制版是一個復雜的系統工程,它涉及到設計、制造、測試等多個環節,每一個環節都需要高水平的技術與團隊的配合。隨著科技的不斷進步,PCB行業也在不斷創新,而這一切都將在未來的電子產品中,繼續為我們帶來更加便捷與高效的生活體驗。PCB的每一塊電路板,仿...

2025-07-14 -

武漢高速PCB培訓功能

武漢高速PCB培訓功能在現代工業和科技迅猛發展的背景下,印刷電路板(PCB)作為電子設備的重要組成部分,其生產和應用已成為一個至關重要的領域。為了更好地適應這一快速變化的環境,PCB培訓正日益成為企業和個人提升技術能力的重要途徑。通過系統的培訓課程,學員們不僅能夠掌握PCB的基本結...

2025-07-14 -

武漢定制PCB制板包括哪些

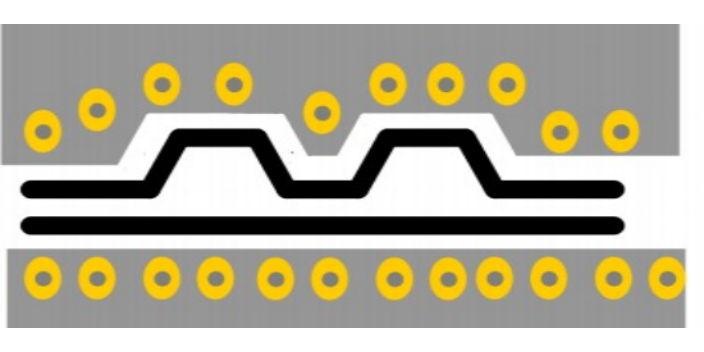

武漢定制PCB制板包括哪些高速 PCB 設計隨著通信技術、計算機技術的不斷發展,電子產品的信號頻率越來越高,對 PCB 的高速設計能力提出了挑戰。高速 PCB 設計需要考慮信號完整性、電源完整性、電磁兼容性等多方面因素,采用先進的設計方法和工具,確保高速信號的可靠傳輸。 綠色 PCB ...

2025-07-13 -

孝感PCB制板價格大全

孝感PCB制板價格大全散熱考慮:對于發熱量較大的元器件,如功率管、集成電路等,應合理布局并預留足夠的散熱空間,必要時可添加散熱片或風扇。抗干擾設計:合理布置地線和電源線,采用多點接地、大面積鋪銅等方法降低地線阻抗,減少電磁干擾。同時,對敏感信號線進行屏蔽處理。PCB布線:線寬和線距...

2025-07-13 -

宜昌打造PCB制版布線

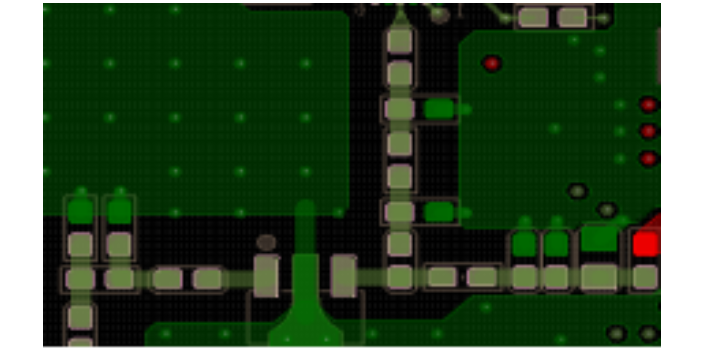

宜昌打造PCB制版布線2.7 測試與檢驗制作完成的 PCB 板需經過嚴格的測試與檢驗,以確保其質量符合標準。常見的測試方法包括外觀檢查,通過肉眼或顯微鏡觀察電路板表面是否存在劃傷、銅箔脫落、絲印模糊等缺陷;電氣性能測試,使用專業的測試設備,如萬用表、示波器、網絡分析儀等,檢測電路板...

2025-07-13 -

荊門PCB制板原理

荊門PCB制板原理接下來,使用顯影液將未固化的油墨清洗掉,露出基材表面。隨后,通過蝕刻工藝,將暴露在外的銅箔腐蝕掉,只留下固化油墨保護下的銅線路,這樣就形成了內層線路的雛形。蝕刻過程需要嚴格控制蝕刻液的濃度、溫度和蝕刻時間,以確保線路的精度和側壁的垂直度。完成蝕刻后,還需要去除...

2025-07-13 -

荊門高速PCB制板銷售電話

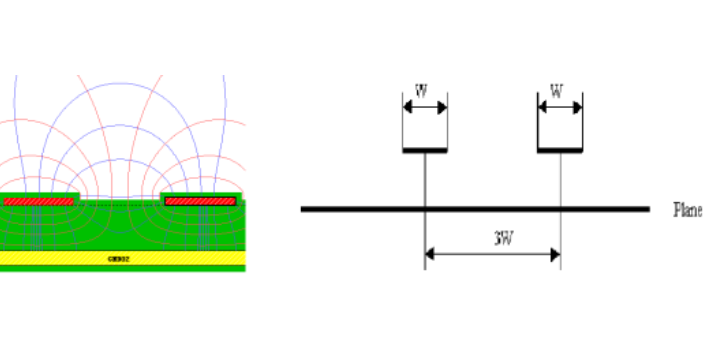

荊門高速PCB制板銷售電話PCB制版的關鍵技術要點線路精度隨著電子產品小型化,線路寬度和間距不斷縮小(如0.1mm以下),需高精度曝光和蝕刻設備。層間對位多層板層間對位精度要求高,通常需使用X-Ray鉆孔和光學對位系統。阻抗控制高速信號傳輸需控制線路阻抗(如50Ω、75Ω),需精確控制...

2025-07-13 -

鄂州焊接PCB制版布線

鄂州焊接PCB制版布線PCB制版,即印刷電路板的制作,是現代電子設備中不可或缺的重要環節。隨著科技的不斷進步,電子產品的性能和功能日益提升,PCB制版技術也在持續演變,以滿足市場對更高效、更小型以及更復雜線路的需求。在PCB制版過程中,首先需要設計電路的布局,這一步驟通常通過專業的...

2025-07-13 -

隨州高速PCB制板走線

隨州高速PCB制板走線設計師們運用專業的EDA(ElectronicDesignAutomation,電子設計自動化)軟件,如AltiumDesigner、CadenceAllegro等,在虛擬世界中構建電路的藍圖。他們需要根據產品的功能需求,合理布局各種電子元器件,規劃信號線和電...

2025-07-13 -

鄂州常規PCB設計布局

鄂州常規PCB設計布局常見問題與解決方案地彈噪聲(Ground Bounce)原因:芯片引腳同時切換導致地電位波動。解決:增加去耦電容、優化地平面分割、降低電源阻抗。反射與振鈴原因:阻抗不匹配或走線過長。解決:端接電阻匹配(串聯/并聯)、縮短關鍵信號走線長度。熱應力導致的焊盤脫落原...

2025-07-13 -

黃岡打造PCB設計價格大全

黃岡打造PCB設計價格大全PCB培訓的**目標在于構建“原理-工具-工藝-優化”的全鏈路能力。初級階段需掌握電路原理圖與PCB布局布線規范,理解元器件封裝、信號完整性(SI)及電源完整性(PI)的基礎原理。例如,高速信號傳輸中需遵循阻抗匹配原則,避免反射與串擾;電源層與地層需通過合理分...

2025-07-13 -

黃石打造PCB設計報價

黃石打造PCB設計報價設計規則檢查(DRC)運行DRC檢查內容:線寬、線距是否符合規則。過孔是否超出焊盤或禁止布線區。阻抗控制是否達標。示例:Altium Designer中通過Tools → Design Rule Check運行DRC。修復DRC錯誤常見問題:信號線與焊盤間距不...

2025-07-13 -

襄陽正規PCB設計怎么樣

襄陽正規PCB設計怎么樣PCB設計注意事項:從基礎規范到避坑指南PCB設計是硬件產品從理論到落地的關鍵環節,其質量直接影響電路性能、生產良率及產品壽命。以下是PCB設計過程中需重點關注的注意事項,涵蓋布局、布線、EMC、可制造性等**環節,助力工程師高效避坑。布局階段:功能分區與散熱...

2025-07-13 -

武漢設計PCB制板銷售

武漢設計PCB制板銷售高速 PCB 設計隨著通信技術、計算機技術的不斷發展,電子產品的信號頻率越來越高,對 PCB 的高速設計能力提出了挑戰。高速 PCB 設計需要考慮信號完整性、電源完整性、電磁兼容性等多方面因素,采用先進的設計方法和工具,確保高速信號的可靠傳輸。 綠色 PCB ...

2025-07-13 -

黃岡設計PCB制版批發

黃岡設計PCB制版批發檢測與測試:完成上述工序后,對 PCB 進行***的檢測與測試。檢測內容包括外觀檢查,查看電路板表面是否有劃傷、銅箔殘留等缺陷;電氣性能測試,使用專業的測試設備,如**測試機,檢測電路板的線路連通性、短路和斷路等問題,確保 PCB 符合設計要求。PCB 制版的...

2025-07-13 -

荊門專業PCB制版批發

荊門專業PCB制版批發隨著智能化、網絡化的浪潮席卷全球,PCB的應用領域也日益***。在物聯網、人工智能、5G通信等新興技術的推動下,PCB行業將迎來巨大的發展機遇。因此,培訓制版已經不僅*是為了技能的掌握,更是為將來的職業發展鋪平道路。總之,PCB培訓制版是一項充滿挑戰與機遇的學...

2025-07-13 -

黃石正規PCB制版

黃石正規PCB制版PCB發展歷程:概述PCB技術從通孔插裝技術(THT)到表面安裝技術(SMT),再到芯片級封裝(CSP)的發展歷程,以及各階段的技術特點和優勢。PCB設計流程需求分析:講解如何確定電路的功能和性能要求,了解電路的工作環境和應用場景,明確PCB的基本要求。原理圖...

2025-07-13 -

鄂州如何PCB設計教程

鄂州如何PCB設計教程規則檢查電氣規則檢查(ERC):利用設計軟件的ERC功能,檢查原理圖中是否存在電氣連接錯誤,如短路、開路、懸空引腳等。設計規則檢查(DRC):設置設計規則,如線寬、線距、元件間距等,然后進行DRC檢查,確保原理圖符合后續PCB布局布線的要求。三、PCB布局元件...

2025-07-13 -

荊州設計PCB設計怎么樣

荊州設計PCB設計怎么樣PCB設計是一個綜合性的工作,涉及電氣、機械、熱學等多方面知識,旨在實現電子電路的功能并確保其可靠運行。以下是PCB設計的主要內容:一、前期規劃需求分析功能需求:明確電路板需要實現的具體功能,例如是用于數據采集、信號處理還是電源控制等。以設計一個簡單的溫度監測...

2025-07-13 -

黃岡正規PCB設計原理

黃岡正規PCB設計原理工具推薦原理圖與Layout:Altium Designer、Cadence Allegro、Mentor PADS。仿真驗證:ANSYS SIwave(信號完整性)、HyperLynx(電源完整性)、CST(EMC)。協同設計:Allegro、Upverte...

2025-07-13 -

十堰什么是PCB設計原理

十堰什么是PCB設計原理電源線和地線布線:電源線和地線要盡可能寬,以降低電源阻抗,減少電壓降和噪聲。可以采用多層板設計,將電源層和地層專門設置在不同的層上,并通過過孔進行連接。特殊信號處理模擬信號和數字信號隔離:在包含模擬和數字電路的電路板中,要將模擬信號和數字信號進行隔離,避免相互...

2025-07-13 -

隨州如何PCB設計

隨州如何PCB設計PCB培訓的**目標在于構建“原理-工具-工藝-優化”的全鏈路能力。初級階段需掌握電路原理圖與PCB布局布線規范,理解元器件封裝、信號完整性(SI)及電源完整性(PI)的基礎原理。例如,高速信號傳輸中需遵循阻抗匹配原則,避免反射與串擾;電源層與地層需通過合理分...

2025-07-13 -

襄陽哪里的PCB設計哪家好

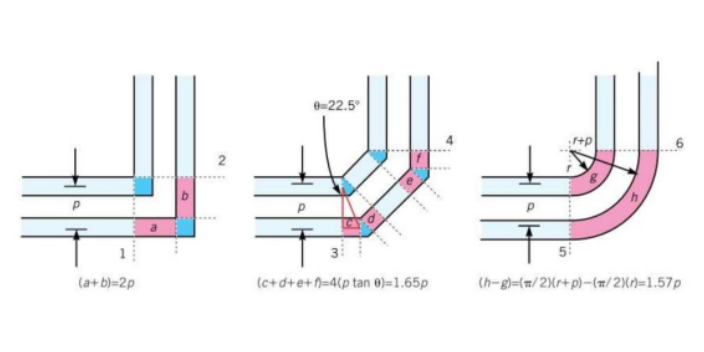

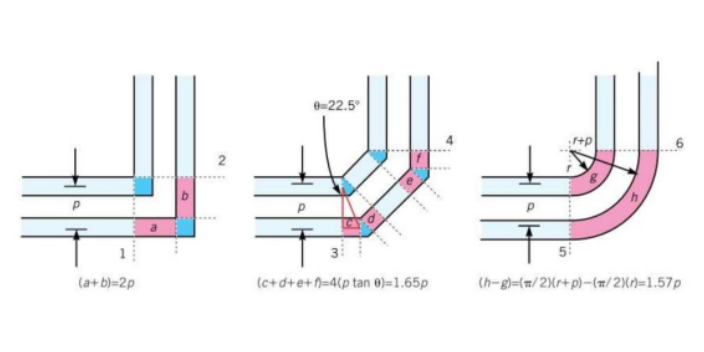

襄陽哪里的PCB設計哪家好PCB布線線寬和線距設置根據電流大小確定線寬:較大的電流需要較寬的線寬以降低電阻和發熱。一般來說,可以通過經驗公式或查表來確定線寬與電流的關系。例如,對于1A的電流,線寬可以設置為0.3mm左右。滿足安全線距要求:線距要足夠大,以防止在高電壓下發生擊穿和短路。...

2025-07-13 -

襄陽印制PCB制板報價

襄陽印制PCB制板報價PCB制板:從設計到實物的精密之旅在現代電子設備高度集成化、小型化的浪潮中,PCB(Printed Circuit Board,印刷電路板)作為電子元器件的支撐體和電氣連接的載體,其重要性不言而喻。一塊質量的PCB不僅是電子產品穩定運行的基礎,更是設計師創意與...

2025-07-13